El interfaces de comunicaciones JTAG, es un acrónimo de Joint Test Action Group, es el nombre común utilizado para la norma IEEE 1149.1 titulada Standard Test Access Port and Boundary-Scan Architecture para test access ports utilizada para testear PCBs utilizando escaneo de límites.

Diseñado originalmente para circuitos impresos, actualmente es utilizado para la prueba de sub-módulos de circuitos integrados, y es muy útil también como mecanismo para depuración de aplicaciones empotradas, puesto que provee una puerta trasera hacia dentro del sistema.

Cuando se utiliza como herramienta de depuración, un emulador en circuito que usa JTAG como mecanismo de transporte permite al programador acceder al módulo de depuración que se encuentra integrado dentro de la CPU. El módulo de depuración permite al programador corregir sus errores de código y lógica de sus sistemas.

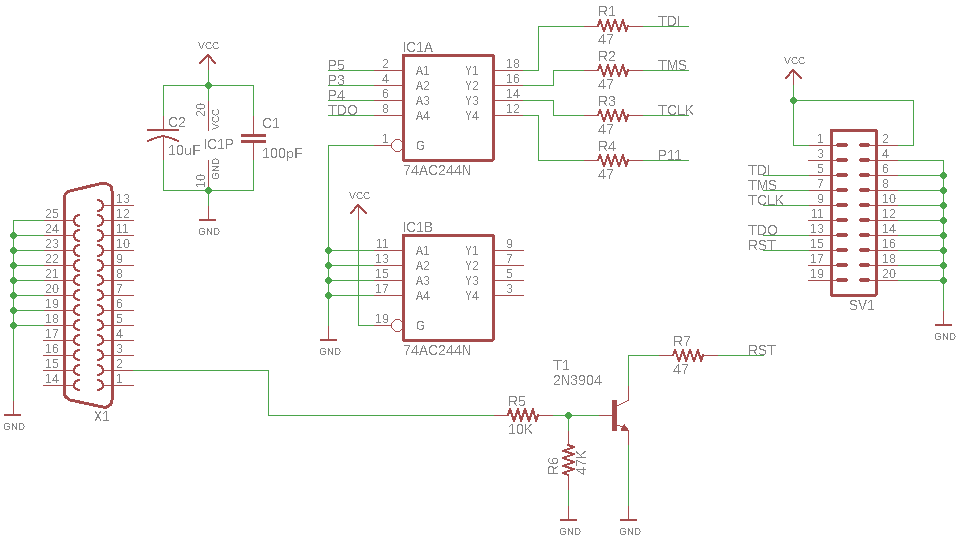

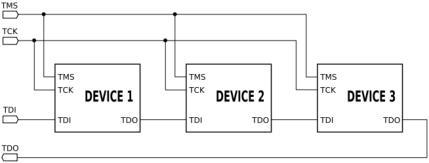

Una interfaz JTAG es un dispositivo especial de cuatro o cinco pines agregadas a un chip, diseñada de tal manera que varios chips en una tarjeta puedan tener sus líneas JTAG conectadas en daisy chain, de manera tal que una sonda de testeo JTAG necesita conectarse a un solo “puerto JTAG” para acceder a todos los chips en un circuito impreso.

Ya que posee una sola línea de datos, el protocolo es necesariamente serial, como el Serial Peripheral Interface.

Se pueden cargar diferentes modo de instrucción como leer el ID del chip, muestrear el valor de pines de entrada/salida, manejar pines de salida, manipular funciones del chip, o funciones de bypass que unen el pin TDI con TDO para lógicamente unir cadenas de varios chips (chips en cascada).

La frecuencia de trabajo de la señal de reloj del pin TCK varía en función de cada chip, pero típicamente está en el rango de 10-100 MHz (10-100ns/bit).

Cuando se hace la operación de boundary scan en circuitos integrados, las señales manipuladas están entre diferentes bloques funcionales del chip, más que entre diferentes chips.

Este sitio web utiliza cookies para que usted tenga la mejor experiencia de usuario. Si continúa navegando está dando su consentimiento para la aceptación de las mencionadas cookies y la aceptación de nuestra política de cookies, pinche el enlace para mayor información.

ACEPTAR